# 100G QSFP28 CWDM4 2km Optical Transceiver Specification

### **Features**

- QSFP28 Serial Optical Interface

- > Supports 103Gb/s data rate

- > 4\*25G CWDM DML Lasers for up to 2km

- > 4 channels PIN detector

- QSFP28 MSA Compliant

- > Compliant with SFF-8679 for electrical interface

- > CAUI-4 High Speed electrical interface

- > Compliant with SFF-8661 for mechanical interface

- > QSFP28 Mechanical Interface for easy removal

- > Duplex LC Receptacle

- > Compliant with SFF-8636 for 2-wire interface for management and DDM

- Support Protocol

- > CWDM4 MSA

- > QSFP28 MSA

- Low Power Consumption

- > Less than 3.5W in temperature range of 0 to 70°C

# **Applications**

- 100G CWDM4 Ethernet links

- Data Center Interconnect

- Infiniband QDR and DDR interconnects

www.luxqlo.com Page 1 of 10

### 1. General Description

L-QSFP28-CWDM4-2 transceiver modules are designed for 100Gigabit Ethernet over 2km single mode fiber. They are compliant with the 100GBASE-CWDM4. Each transceiver incorporates four direct modulated lasers with driver ICs, four PIN diodes with TIAs, and two Mux/De-Mux blocks in a highly integrated CWDM4 configuration for operation over duplex LC connectors. Mechanical dimensions, connectors and the footprint of this product is QSFP28 specifications compliant. Digital Diagnostics functions are available via a 2-wire serial interface, as specified SFF-8636.

# 2. Absolute Maximum Ratings and Recommended Operating Conditions

**Table 2.1 Absolute Maximum Ratings**

| Parameter                                  | Symbol    | Min  | Max | Unit |

|--------------------------------------------|-----------|------|-----|------|

| Storage Temperature                        | Tst       | -40  | 85  | °C   |

| Relative Humidity (non-condensation)       | RH        | 5    | 95  | %    |

| Supply Voltage                             | VccR/VccT | -0.5 | 3.6 | V    |

| Damage Threshold, each Lane <sup>[1]</sup> | THd       | 3.5  | -   | dBm  |

**Table 2.2 Recommended Operating Conditions**

| Parameter                         | Symbol    | Min   | Max   | Unit |

|-----------------------------------|-----------|-------|-------|------|

| Operating Case Temperature        | Торс      | 0     | 70    | °C   |

| Relative Humidity(non-condensing) | Rhop      | 5     | 85    | %    |

| Power Supply Voltage              | VccR/VccT | 3.135 | 3.465 | V    |

| Power Supply Current              | Irt       | -     | 1050  | mA   |

| Total Power Consumption           | Pc        | -     | 3.5   | W    |

www.luxqlo.com Page 2 of 10

# 3. Optical Specifications

### 3.1 Optical Transmitter

**Table 3.1 Transmitter Optical Interface**

| Para                           | meter              | Symb                 | Min    | Typic  | Max    | Unit |

|--------------------------------|--------------------|----------------------|--------|--------|--------|------|

|                                |                    | ol                   |        | al     |        |      |

| Data rate per channel          | 100G Base<br>CWDM4 |                      |        | Gbps   |        |      |

|                                |                    | LO                   | 1264.5 | 1271   | 1277.5 | nm   |

| Center Waveleng                | th                 | L1                   | 1284.5 | 1291   | 1297.5 | nm   |

| osme mareneng                  | •••                | L2                   | 1304.5 | 1311   | 1317.5 | nm   |

|                                | L3                 | 1324.5               | 1331   | 1337.5 | nm     |      |

| Side Mode Suppression Ratio    |                    | SMSR                 | 30     |        |        | dB   |

| Total Average La               | unch Power         | P <sub>T</sub>       |        |        | 8.5    | dBm  |

| Average launch p               | ower, each Lane    | P <sub>avg</sub>     | -6.5   |        | 2.5    | dBm  |

| OMA, each lane                 |                    | Рома                 | -4     |        | 2.5    | dBm  |

| Transmitter and d              | ispersion penalty  | TDP                  |        |        | 3      | dB   |

| Average launch power of Tx OFF |                    | P <sub>ave_off</sub> |        |        | -30    | dBm  |

| Extinction ratio               |                    | ER                   | 3.5    |        |        | dB   |

| Optical Power for              |                    |                      |        | -30    | dBm    |      |

| Transmitter Refle              | ctance             |                      |        |        | -12    | dB   |

www.luxglo.com Page 3 of 10

### 3.2 Optical Receiver

**Table 3.2 Receiver Optical Interface**

| Pa                          | rameter                                                       | Symb<br>ol | Min    | Typic<br>al | Max    | Unit |

|-----------------------------|---------------------------------------------------------------|------------|--------|-------------|--------|------|

| Data rate<br>per<br>channel | 100G Base<br>CWDM4                                            |            |        | 25.78125    |        | Gbps |

|                             |                                                               | L0         | 1264.5 | 1271        | 1277.5 | nm   |

| Center Wa                   | velenath                                                      | L1         | 1284.5 | 1291        | 1297.5 | nm   |

|                             | Contor Wavelength                                             |            | 1304.5 | 1311        | 1317.5 | nm   |

|                             |                                                               | L3         | 1324.5 | 1331        | 1337.5 | nm   |

| _                           | Average receiver power, each lane <sup>[1]</sup>              |            | -11.5  |             | 2.5    | dBm  |

| Sensitivi                   | 100G Base<br>CWDM4, OMA<br>per lane <sup>[2]</sup>            |            |        |             | -10    | dBm  |

| ty -                        | Stressed receiver sensitivity (OMA), each lane <sup>[3]</sup> |            |        |             | -7.3   | dBm  |

| Rx LOS                      | Assert Rx LOS                                                 |            | -24    |             |        | dBm  |

|                             | De-assert                                                     |            |        |             | -11.6  | dBm  |

|                             | Hysteresis                                                    |            | 0.5    |             |        | dB   |

| Receiver R                  | eflectance                                                    |            |        |             | -26    | dB   |

#### Notes:

- 1. Minimum value is informative, equals min TxOMA with infinite ER and max channel insertion loss

- 2. Receiver sensitivity is measured with conformance test signal for BER=5x10<sup>-5</sup>.

- 3. Measured with conformance test signal at TP3 for BER = 5x10-5

# 4. Electrical Specifications

**Table 4.1 High Speed Electrical Specifications**

| Parameters                     | Min   | Typic al | Max   | Unit |

|--------------------------------|-------|----------|-------|------|

| Signaling rate per lane        |       | 25.78125 |       | Gbps |

| Supply voltage                 | 3.135 |          | 3.465 | V    |

| Input differential impedance   |       | 100      |       | Ω    |

| Differential data input swing  | 190   |          | 1000  | mV   |

| Differential data output swing | 300   |          | 900   | mV   |

Table 4.2 2-wire Electrical Specifications

| rable 4.2 2-wire Electrical Opecifications |             |             |             |      |  |

|--------------------------------------------|-------------|-------------|-------------|------|--|

| Parameter                                  | Symbol      | Min         | Max         | Unit |  |

| Host 2-wire Vcc voltage                    | Vcc_Host_2w | 3.14        | 3.46        | V    |  |

|                                            | Vol         | 0.0         | 0.40        | V    |  |

| SCL and SDA Voltage <sup>[1]</sup>         |             | Vcc_Host_2w | Vcc_Host_2w |      |  |

|                                            | Vон         | -0.5        | +0.3        | V    |  |

|                                            | VIL         | -0.3        | VccT*0.3    | V    |  |

|                                            | ViH         | VccT*0.7    | VccT+0.5    | ٧    |  |

| Input current on the SCL and SDA contacts  | lı          | -10         | 10          | mA   |  |

Notes:

1. These voltages are measured on the other side of the connector to the device under test

www.luxglo.com Page 5 of 10

#### 5. User Interface

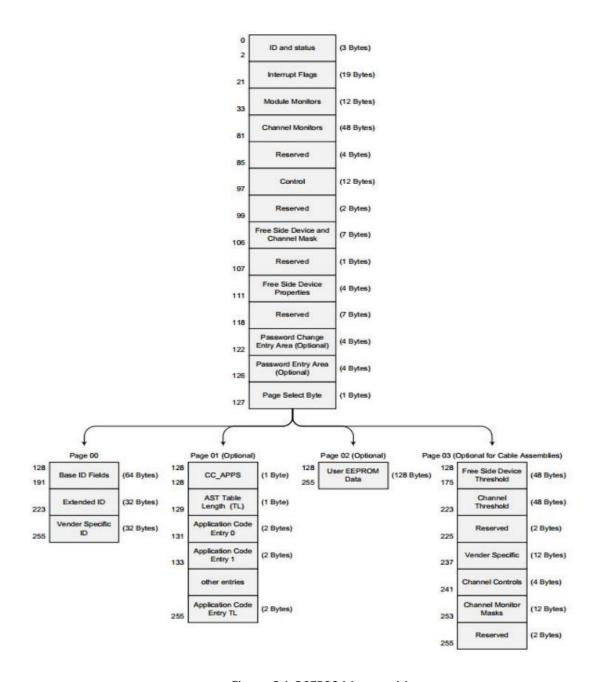

#### 5.1 Management Interface

2-Wire Serial Address: 1010000x (A0H)

Figure 6.1 QSFP28 Memory Map

www.luxglo.com Page 6 of 10

#### **5.2 Digital Diagnostic Monitor Accuracy**

The following characteristics are defined over recommended operating conditions.

**Table 6.2 Digital Diagnostic Monitor Accuracy**

| Parameter                                      | Accuracy | Unit |

|------------------------------------------------|----------|------|

| Internally Measured Transceiver Temperature    | ±3       | °C   |

| Internally Measured Transceiver Supply Voltage | ±3       | %    |

| Measured Tx Bias Current                       | ±10      | %    |

| Measured Tx Output Power                       | ±2       | dB   |

| Measured Rx Received Average Optical Power     | ±2       | dB   |

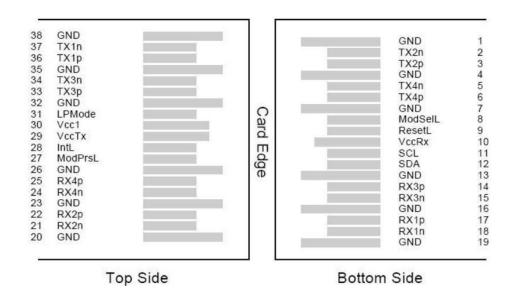

## 6. Pin Assignment and Pin Description

#### 6.1 PIN Definitions

QSFP28 transceiver pad layout, host PCB QSFP28 pinout, and PIN descriptions are as follows:

Figure 6.1 QSFP28 Transceiver Electrical Pad layout

www.luxglo.com Page 7 of 10

#### **6.2 PIN Description**

**Table 7.2 Pin Description**

| Pin | Logic      | Symbol  | Description                         | Plug Sequence | Notes |

|-----|------------|---------|-------------------------------------|---------------|-------|

| 1   |            | GND     | Ground                              | 1             | 1     |

| 2   | CML-I      | Tx2n    | Transmitter Inverted Data Input     | 3             |       |

| 3   | CML-I      | Tx2p    | Transmitter Non-Inverted Data Input | 3             |       |

| 4   |            | GND     | Ground                              | 1             | 1     |

| 5   | CML-I      | Tx4n    | Transmitter Inverted Data Input     | 3             | 3     |

| 6   | CML-I      | Tx4p    | Transmitter Non-Inverted Data Input | 3             | 3     |

| 7   |            | GND     | Ground                              | 1             | 1     |

| 8   | LVTTL-I    | ModselL | Module Select                       | 3             |       |

| 9   | LVTTL-I    | ResetL  | Module Reset                        | 3             |       |

| 10  |            | Vcc Rx  | +3.3V Power Supply Receiver         | 2             | 2     |

| 11  | LVCMOS-I/O | SCL     | 2-wire serial interface clock       | 3             |       |

| 12  | LVCMOS-I/O | SDA     | 2-wire serial interface data        | 3             |       |

| 13  |            | GND     | Ground                              | 1             | 1     |

| 14  | CML-O      | Rx3p    | Receiver Non-Inverted Data Output   | 3             | 3     |

| 15  | CML-O      | Rx3n    | Receiver Inverted Data Output       | 3             | 3     |

| 16  |            | GND     | Ground                              | 1             | 1     |

| 17  | CML-O      | Rx1p    | Receiver Non-Inverted Data Output   | 3             |       |

| 18  | CML-O      | Rx1n    | Receiver Inverted Data Output       | 3             |       |

| 19  |            | GND     | Ground                              | 1             | 1     |

| 20  |            | GND     | Ground                              | 1             | 1     |

| 21  | CML-O      | Rx2n    | Receiver Inverted Data Output       | 3             |       |

| 22  | CML-O      | Rx2p    | Receiver Non-Inverted Data Output   | 3             |       |

| 23  |            | GND     | Ground                              | 1             | 1     |

| 24  | CML-O      | Rx4n    | Receiver Inverted Data Output       | 3             | 3     |

| 25  | CML-O      | Rx4p    | Receiver Non-Inverted Data Output   | 3             | 3     |

| 26  |            | GND     | Ground                              | 1             | 1     |

| 27  | LVTTL-O    | ModPrsL | Module Present                      | 3             |       |

| 28  | LVTTL-O    | IntL    | Interrupt                           | 3             |       |

| 29  |            | Vcc Tx  | +3.3V Power supply transmitter      | 2             | 2     |

| 30  |            | Vcc1    | +3.3V Power supply                  | 2             | 2     |

| 31  | LVTTL-I    | LPMode  | Low Power Mode                      | 3             |       |

| 32  |            | GND     | Ground                              | 1             | 1     |

| 33  | CML-I      | Tx3p    | Transmitter Non-Inverted Data Input | 3             | 3     |

| 34  | CML-I      | Tx3n    | Transmitter Inverted Data Input     | 3             | 3     |

| 35  |            | GND     | Ground                              | 1             | 1     |

| 36  | CML-I      | Tx1p    | Transmitter Non-Inverted Data Input | 3             |       |

| 37  | CML-I      | Tx1n    | Transmitter Inverted Data Input     | 3             |       |

| 38  |            | GND     | Ground                              | 1             | 1     |

#### Note:

[1] GND is the symbol for signal and supply (power) common for the QSFP28 module. All are common within the QSFP28 module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

[2] Vcc Rx, Vcc1 and Vcc Tx are the receiver and transmitter power supplies and shall be applied concurrently.

www.luxglo.com Page 8 of 10

#### 6.3 Multiplex LPMode and IntL

The LPMode PIN is multiplexed for TX\_Disable and IntL PIN multiplexed for Rx\_LOS according to customers' requirements

Table 6.3 Multiplex LPMode and IntL table

|      | LPMode      | TX_Disable  | IntL        | RX_LOS      |

|------|-------------|-------------|-------------|-------------|

| High | Asserted    | Asserted    | De-asserted | Asserted    |

| Low  | De-asserted | De-asserted | Asserted    | De-asserted |

Following MSA's design concept, when a new control feature is added, there should be two fields to define for the new feature, advertise (Read-Only) field to indicate if the feature is supported, and control field (R/W) to configure the new feature. In SFF8636, most of register in page 0 low are defined as R/W registers. Most register in page 0 high are defined as Read-Only registers.

Table 6.4 Definition of configuration register for Multiplex function

|           |       | ingulation register for infultiplex function |

|-----------|-------|----------------------------------------------|

| Registers | State | Description                                  |

|           |       |                                              |

| 0         |       | IntL pin only. RX_LOS pin not supported.     |

| Bit 0     |       |                                              |

|           | 1     | Both IntL and RX_LOS supported.              |

|           |       |                                              |

|           | 0     | LPMode pin only. TX Disable not supported.   |

| Bit 1     |       |                                              |

| 1         |       | Both LPMode and TX Disable supported         |

|           |       |                                              |

Table 6.5 Definition of control register for Multiplex function

| Registers | State       | Description       |

|-----------|-------------|-------------------|

| Bit 0     | 0           | IntL pin active   |

|           | 1 (Default) | RX_LOS active     |

| Bit 1     | 0           | LPMode pin active |

|           | 1 (Default) | TX Disable active |

#### Note:

Register is read-only during high power mode and can only be modified at lower power mode.

www.luxglo.com Page 9 of 10

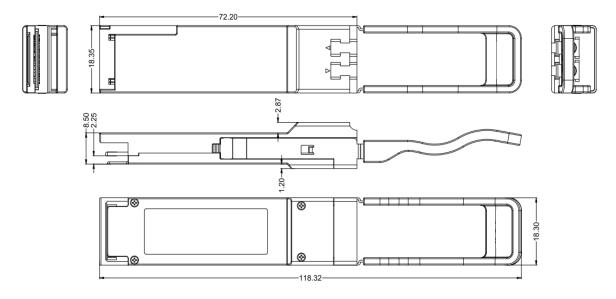

# 7. Package Dimensions

Figure 7.1 shows the package dimensions of the module. The module is designed to be complaint with QSFP28 MSA specification. Package dimensions are specified in SFF-8661.

### 9.2 Electromagnetic Compatibility

All transceivers are designed to meet FCC Class B limits.

# 8. Ordering Information

| Part Number          | Temperature<br>Range | Distance | Fiber<br>Type | E/O                                         | O/E |

|----------------------|----------------------|----------|---------------|---------------------------------------------|-----|

| L-QSFP28-<br>CWDM4-2 | 0°C to + 70°C        | 2km      | SMF           | DFB<br>1271nm<br>1291nm<br>1311nm<br>1331nm | PIN |

www.luxglo.com Page 10 of 10